Onderzoekscentrum imec werkt samen met chipfabrikanten TSMC en Intel aan een belangrijke stap richting de toekomst van chiptechnologie: de integratie en opschaling van 2D-materialen. Deze ultradunne materialen, slechts enkele atoomlagen dik, bieden nieuwe mogelijkheden om de grenzen van chipminiaturisatie te verleggen.

Op IEDM 1975, precies vijftig jaar geleden, voorspelde Gordon Moore – toen aan het hoofd van chipmaker Intel – dat het aantal transistoren op een chip elke twee jaar zal verdubbelen. Sindsdien is die voorspelling beroemd geworden als de ‘Wet van Moore’ en uitgegroeid tot een selffulfilling prophecy.

Fysieke grenzen

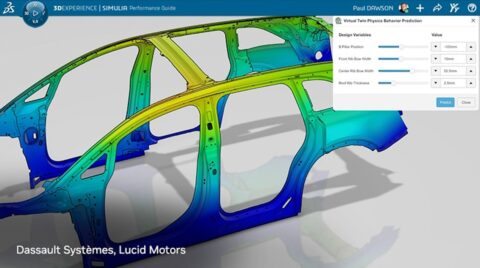

De komende jaren zal de klassieke miniaturisatie van siliciumchips, gedreven door die Wet van Moore, op fysieke grenzen botsen. Transistoren kunnen niet eindeloos kleiner worden zonder dat lekstromen en kwantumeffecten de werking verstoren. Om de groeiende vraag naar rekenkracht – onder meer voor artificiële intelligentie – in de toekomst te blijven beantwoorden, is de industrie nu al aan het zoeken naar nieuwe materialen en transistorarchitecturen.

2D-materialen to the rescue?

Een beloftevolle piste zijn 2D-materialen. Deze materialen zijn extreem dun – slechts één of enkele atoomlagen. Dat maakt ze veelbelovend als geleidingskanaal in toekomstige chips, ter vervanging van het siliciumkanaal dat steeds moeilijker te verkleinen is. Maar hun grote voordeel vormt tegelijk ook de grote uitdaging: het is technisch bijzonder moeilijk om zulke dunne lagen uniform aan te brengen op siliciumwafers en te integreren in bestaande productieprocessen.

Van lab naar fab

Vijftig jaar na de beroemd geworden presentatie van Gordon Moore op IEDM presenteren onderzoekers van imec op diezelfde conferentie twee papers die de uitdagingen rond 2D-materialen aanpakken. In samenwerking met TSMC ontwikkelde imec p-type transistoren (pFETs) op basis van wolfraamdiselenide (WSe₂). Deze 2D-transistoren leveren recordprestaties en zijn gemaakt met een proces dat compatibel is met bestaande chipproductie, wat het potentieel van 2D-materialen voor toekomstige chiparchitecturen toont.

Integratie van 2D-materialen

Parallel werkte imec aan technieken die de integratie van 2D-transistoren in industriële productie mogelijk maken. Tot nu toe bleven resultaten immers vooral beperkt tot laboratoriumexperimenten op individuele testchips. Om 2D-materialen industrieel relevant te maken, moeten deze processen worden opgeschaald naar 300mm-wafers. Dit is het standaardformaat van siliciumschijven waarop de industrie in massa chips produceert. Daarnaast moeten betrouwbaarheid en uniformiteit worden gegarandeerd. Daarom ontwikkelde imec samen met Intel nieuwe technieken om de basiscomponenten van 2D-transistoren (kanaal, contacten, poort en diëlektricum) efficiënter te integreren in massaproductieprocessen.

Verdere optimalisatie is nodig, maar deze nieuwe verwezenlijkingen tonen aan dat het mogelijk is om de belofte van 2D-materialen om te zetten in realiteitGouri Sankar Kar, vice president R&D compute & memory device technologies bij imec

Optimalisatie nodig

“Verdere optimalisatie is nodig, maar deze nieuwe verwezenlijkingen tonen aan dat het mogelijk is om de belofte van 2D-materialen om te zetten in realiteit. In samenwerking met wereldspelers als TSMC en Intel zet imec cruciale stappen richting industriële toepassing van deze materialen”, zegt Gouri Sankar Kar, vice president R&D compute & memory device technologies bij imec.

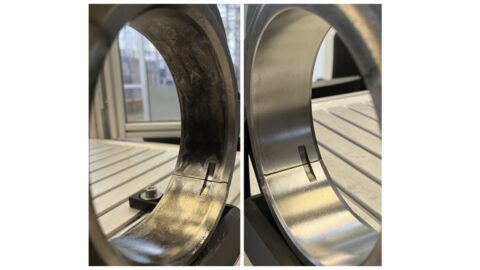

Cleanroom van imec

In het begin van deze eeuw lanceerde imec een baanbrekend 300 mm-onderzoeksprogramma. Sindsdien is de cleanroom in Leuven, België, snel uitgegroeid tot een belangrijk knooppunt van het wereldwijde halfgeleider-ecosysteem. Hier worden de processen die de toekomstige microchiptechnologie mogelijk maken, gezamenlijk ontwikkeld en geperfectioneerd. Daartoe is de 8.000 m² grote cleanroomruimte gevuld met ’s werelds meest geavanceerde, voor de industrie relevante apparatuur – van alle toonaangevende OEM’s, waaronder veel Europese leveranciers – voor lithografie, implantatie, reiniging, metrologie, depositie, enz.

Dankzij financiering van de EU Chips Act is de 300 mm-infrastructuur van imec uitgebreid met een nieuwe cleanroom en tientallen extra geavanceerde tools voor verwerking en metrologie. De efficiëntie van de fabrieksactiviteiten wordt hiermee naar een hoger niveau worden getild door meer automatisering van tools, meer verbonden instrumenten met centrale gegevensopslag en geautomatiseerde verbindingen tussen de opslagplaatsen.

Foto: stof- en trillingsvrije laboratorium van imec waar de 2D-materialen aangebracht worden op 300mm-wafers (foto: imec)

Bron: imec

Lees ook: Nieuwe hightech proeffabriek voor fotonische chips in de startblokken